Xilinx DDS Compilerを使ってみた-1-

AM送信波の元となる搬送波をDDS Compilerで作成してみる。

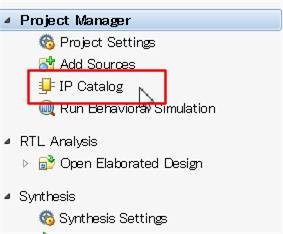

いつも通りPlanAheadを立ちあげてIPを追加します。

Project Managerの所にある「IP Catalog」を選択

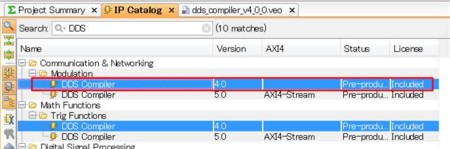

IP Catalogが表示されたら、Searchに「DDS」を入力すると

DDS Compilerが出てくる。

今回はAXIに接続しないIPを使うので4.0の方をダブルクリック

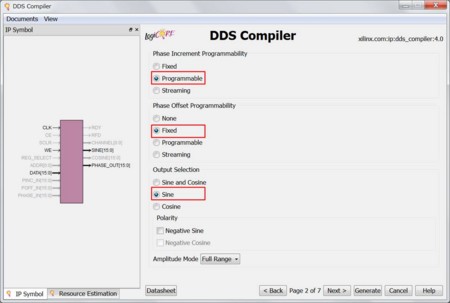

これからDDSの設定をしていく。

System Clockは10MHz

Output Width 16bit

中波の音質を考えるとここまで必要ではないと思うが一応16bitにしておく。

Phase Incrementは周波数を可変にするので「Programmable」にする。

Phase Offsetは必要ないのでFixid

Output Selectionはサイン波だけあれば良いので「Sine」を選択

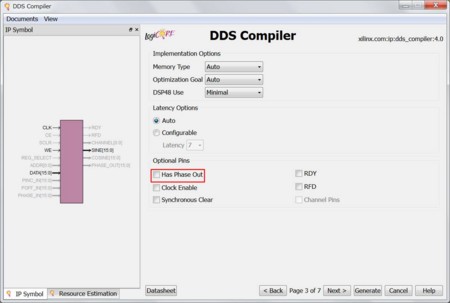

Phase Out出力は必要ないのでチェックを外す

Nextを何回か押すと一覧が表示される。

問題なければ「Generate」でIPを生成する。

これでIPが生成される。

次にIPをインスタンスする方法を記載する。

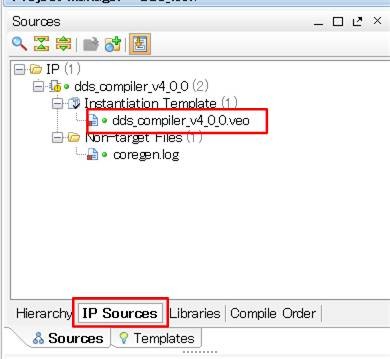

「IP Sources」の中に.veoというファイルがあり

これがインスタンスするテンプレートファイルになっている。

開くと以下記述があるのでこれを使う

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG dds_compiler_v4_0_0 your_instance_name ( .clk(clk), // input clk .we(we), // input we .data(data), // input [15 : 0] data .sine(sine) // output [15 : 0] sine ); // INST_TAG_END ------ End INSTANTIATION Template ---------

さくっとテストベンチ書いて動作させたのが以下波形

dataとweで加算量を指定するとsineから値が出力される。

遅延量は特に指定していないので9Clockになっている。