Fedora18をVMWare Playerでインストールしてみた。

VMware Player上にFedora18をインストールしたのでメモ。

結構はまってしまったのでその辺を適当にまとめています。

使用バージョンはVMWare Player 5.0.1

Fedoraのディスクは現在公開されているFedora-18-x86_64-Live-Desktop.iso

- 仮想PCの設定

バージョンはFedora 64bit

この画面で「ハードウェアをカスタマイズ」を選択

ディスプレイを選択し「3Dグラフィックスのアクセラレーション」をOFFにする。

※これをしないとCDブート時にフリーズする。

- OSインストール

これで仮想PCの設定は完了。パワーオンします。

「live system user」でログイン後「Install to Hard Drive」を選択。

インストール先に警告マークがついているのでクリック

続行を押すと何かウィンドウが出てきますがとりあえずそのまま続行

これで警告マークが消えます。

インストールが終わるとこの画面になります。

警告マークがついた項目が見つからないのは解像度が小さいからです。

fedoraのシステム設定で1024x768にするとrootパスワード設定が出てきます。

(これに気づかず無理やりリブートしたらHDDブート後ログイン画面でログインできず再インストールしました。)

rootのパスワードを設定後再起動すればインストールできました。

HDDブート後の設定は特筆すべき点はなかったので省略。

- vmware toolsのインストール

端末を立ちあげ以下順で設定。

アップデート

sudo yum update

念のためカーネルのアップデート & 再起動

sudo yum update karnel sudo reboot

必要なパッケージをインストール

sudo yum install gcc sudo yum install kernel-headers kernel-devel

3.7.2-201.fc18.x86_64以降でvmware toolsをインストールする時にkernel headerが見つからずインストールできない不具合があるので必要なファイルをあらかじめコピー

パス内に入っているkernelのバージョンは「uname -r」で取得しています。

sudo cp /usr/src/kernels/`uname -r`/include/generated/uapi/linux/version.h /lib/modules/`uname -r`/build/include/linux/

後はvmware toolsを解凍してインストールします。

vmware toolsをマウントした後のファイルは以下にありますので適当な場所へコピー

/run/media/ユーザー名/VMware\ Tools/VMwareTools-9.2.2-893683.tar.gz

インストルコマンド

./vmware-install.pl

インストールが終わったら再起動で完了!

Microsoft VisioをCADとして使ってみた。

前回フリーのCADツールを幾つか書きましたが

私にとっては大変使いづらく別のツールを使うことにします。

という訳で仕事で良く使っているMicrosoft Visioを使って図形を描いてみました。

VisioはDXFファイルで保存できますがそのまま保存してもNCVCで読めませんでした。

試行錯誤の結果NCVCでGコードを出力できたのでメモ。

(※以下手順はVisio2010を使用しています。)

今回は材料に溝を彫って切り出す加工の図面を書きます。

(アクリル板を加工して下からライトアップしようと思ってます。)

1.図面を書く

Visioで図面を書く際に気をつける事は使える図形が限られている点です。

私が試してGコードまで生成出来た図形は以下です。

- 四角形

- 楕円

- 直線

- 円弧

- 鉛筆

出来なかった図形は以下です。

- 自在曲線→NCVCに持って行くとエラーになります。(スプライン曲線に対応していない?)

- 文字→こちらもエラーになります。

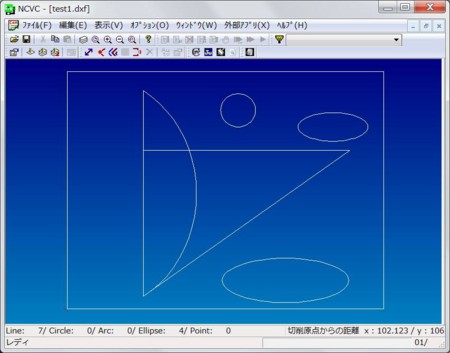

適当に図形を書いたのが以下になります。縮尺は1:1で1mmグリッドを表示しています。

緑の四角は材料を切り出すライン左下の小さな丸は原点を表しています。

(NCVCでは原点を丸で表します。)

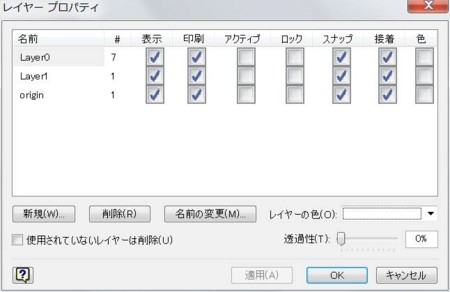

2.Visioでレイヤーを作成する。

「ホーム→レイヤー→レイヤープロパティ」を選択して

レイヤーを作成します。最低限Layer0とoriginがあればOK

Layer毎にZ軸の深さを変えれます。

私は以下の様にしました。

- origin:原点

- Layer0:溝を彫る

- Layer1:深彫りで材料を切り出す。

3.図形をレイヤーに割り振る。

レイヤーを作成したら各レイヤーに図形を振り分けます。

切り出しラインの中にある図形を範囲選択して「ホーム→レイヤー→レイヤーに割り当て」

を選択すると作成したレイヤーが表示されるのでLayer0にチェックを入れてOK

同様に左下の丸をorigin。切り出しラインをLayer1にします。

4.DXF形式で保存

DXF形式で保存します。

保存後NCVCで開くと図面が表示されます。

これでVisioからNCVC用のDXFファイルを生成出来ました。

次はNCVCの設定をします。

CNCの使い方について調べてみた

前回切削をすると書きましたがその前に

そもそも図面からCNCをどう動かすかを調べてみました。(今更・・・)

以下手順で作成していく様です。

CADといえばAutoCADが有名ですが値段が高いので他のCADを使います。

フリーだと以下のCADがあります。

- Jw_cad

- AR_CAD

- 鍋CAD

NCVCが扱えるファイルにDXFというAutoCADが使用しているフォーマットがあります。

このフォーマットはCADだけではなくドローツールでも対応している事があるので

DXFに対応したツールを使います。

(Jw_cadのファイルならNCVCはそのまま読めますがJw_cadの扱いが難しかったので使ってないです)

次にNCVCというツールで図面からGコードというCNCを制御するコードを生成します。

上記CADは2次元CADなので平面データしか作成できません。NCVC上でZ軸(深さ)方向の設定をします。

最後にMach3というツールでCNCを制御します。

フリー版ではGコード500行までしか動作しません。

曲線を使うとあっという間に500行超えます・・・

大体の流れはこの様になっています。

次回はCADについてメモします。

格安CNCを買ってみた。- Sable-2015 -

新年あけましておめでとうございます。年末更新出来なかったので・・・

(やったことは12月中旬~下旬の出来事)

FMCメザニンボードを設計してみた-その1-

で腹案があると言いましたがそれがこちら

http://cncmill.web.fc2.com/

Sable-2015というCNCフライス盤です。これで銅箔基板の表面を削り基板を作成します。

これの良い所は穴あけも自動化出来る点です。

回路図CADからCNC制御までの手順はネットで公開されている方がいますので

実際に作成する時にでもメモします。

注文は上記HPから注文しました。注文時に彫刻カッターとエンドミルも追加。

注文から2週間程で受け取りました。

で、設置したのが↓

切削屑が飛んでも良いようにダンボールの中にいれました。

それとCNCの足にはダイソーで売っていた耐震用のゴム板(?)をはさみました。

捨て板はとりあえず適当な発泡スチロールを両面テープで固定。

困ったのがPCと接続する時でした。

Sable-2015はパラレルポート接続なので少し古いマシンではないとついていません。

それとOSが64bitでは仕様出来ないようなので、Vista搭載の中古PCを買って来ました。

(Vistaはあまりにも重かったのでXPにダウンロードしました・・・)

Core2Duo世代で7980円となかなかお買い得でした。

接続さえ出来れば付属のマニュアルを参照して設定するだけです。

では、次は何か切削してみます。

FMCメザニンボードを設計してみた-失敗-

EAGLEで配線図はできたのでレイアウトをやります。

EAGLEのフリー版では100x80mm 2層までです。

この範囲でまずはやってみます。

右の白い四角が100x80の箱で左側がレイアウト予定の部品です。

この時点で無理な気がします・・・

Routing Grid 10milで実行してみる。

途中で自動配線が止まってしまいました・・・

まあ160ピン全部使うことはないから一部だけ使うとして

どのくらいまで減らせばいいか見てみます。

SystemCで廃止/廃止予定の機能を調べてみた

SystemC Advent Calendar2012 の 23日目(になるかも?)の記事です。

よろしくおねがいします。

SystemCのバージョンアップに伴って削除された機能や推奨されない機能

がどのくらい過去にあったか調べてました。古いコードを見た際に参考にするメモです。

(リリースノートから抜粋しています。すべて網羅できてないと思います・・・)

現在accelleraにはSystemC 1.0.2まで古いコードが置かれています。

今回は2.x系(2.0から2.3)まで追ってみました。

2.0(2002-02-08) -> 2.0.1(2002-04-11)

- 値

sc_logic sc_logic_dat1; //2.3でもコンパイル可 sc_logic_dat1 = sc_logic_0; //2.0以降 SC_LOGIC_0 に変更 sc_logic_dat1 = sc_logic_1; //2.0以降 SC_LOGIC_1 に変更 sc_logic_dat1 = sc_logic_Z; //2.0以降 SC_LOGIC_Z に変更 sc_logic_dat1 = sc_logic_X; //2.0以降 SC_LOGIC_X に変更

- 型変換

//2.0まで(2.3でコンパイルエラー) cout << "sc_lvjdat8(signed) = " << sc_lv_dat8.to_signed() << end; cout << "sc_lv_dat8(unsigned) = " << sc_lv_dat8.to_unsigned() << endl; //2.0以降 cout << "sc_lv_dat8(signed) = " << sc_lv_dat8.to_int() << endl; cout << "sc_lv_dat8(unsigned) = " << sc_lv_dat8.to_uint() << endl;

- データタイプ

sc_bit bit_dat1 = 0; //2.0で廃止 bool bit_dat1 = 0; //2.0以降はbool型を使う

- 演算

//2.3でコンパイルエラー sc_logic_dat1 = !sc_logic_dat1: //2.0ではsc_logicの!演算子が削除された sc_logic_dat1 = ~sc_logic_dat1: //反転時は~演算子を使う

- ビット幅取得

//2.3でコンパイルエラー cout << "sc_lv_dat8 width = " << sclv_dat8. bitwidth() << endl; //2.0削除 cout << "sc_lv_dat8 width = " << sc_lv_dat8. length() << endl; //2.0から

- sensitive

//2.3でコンパイルエラー sensitive_pos << clk; //2.0廃止 sensitive_neg << clk; //2.0廃止 sensitive << clk.pos(); //2.0以降 sensitive << clk.neg(); //2.0以降

- その他

2.0.1のリリースノートにはSC_CTHREADは推奨されないと書かれています。

(当時のSystemC入門書とかを読むと、推奨しないとなっている事があります。)

当時はSC_THREADとSC_METHODで置き換えれるようにするつもりだったようです。

もちろんSystemC2.3では使えますし、高位合成ツールとかで使われているのを見ると

当分廃止はされないと思います。

ちなみにこの記事を書こうと思った理由はこのSC_CTHREADっていつ無くなるって

話だったかな?と思ったのがきっかけです。

2.0.1(2002-04-11) -> 2.1(2005-09-20)

- データ型

sc_string string_dat; //2.1で廃止(2.3でコンパイルエラー) sc_string_old string_dat; // sc_string_oldかstringで代替 string string_dat; sc_pvector<unsigned int> vector_dat //vector型で置き換えれるように std::vector<unsigned int > vector_dat; //なっていますが2.3でも使えます。

- その他

sc_cycle() 2.3でコンパイルエラー

sc_create_isdb_file() ISDBフォーマット削除。(2.3でエラー)

ISDB形式ってどの波形ビューワで見れたのでしょうか?

2.1(2005-09-20) -> 2.2(2007-03-14) -> 2.2(2007-03-14)

2.2は2つ公開されていますのでまとめています。

watching(reset,delayed() == false); //2.2で削除(2.3でコンパイルエラー) reset_signal_is(reset,false); //2.1で追加 wait_until( valid.deferred() == true ); //2.2で削除(2.3でコンパイルエラー) //deferred()も削除 do { wait(); } while ( !(valid == true) );//こっちに置き換える

- その他

end_module() 削除予定?

2.2(2007-03-14) -> 2.3(2012-03-14)

機能追加はあるけどリリースノートを読む限り削除はなさそう・・・

今回は廃止された機能について調べてました。

これを修正すれば古いコードのコンパイルはできそうです。

しかし、バージョンによってシミュレーション結果が変わるという話を

聞いた事がありますので。そこは気をつける必要があります。

FMCメザニンボードを設計してみた-その1-

FMCコネクタが届いたので使えるようにボードを設計してみる。

使いやすいように2.57mmピンヘッダに変換するボードを作る予定です。

購入したコネクタは1.27mmピッチなのでなんとかなりそうです。

今のところ以下の選択肢

- ユニバーサル基板で作る

ハーフピッチのユニバーサル基板は入手可能なので有力候補。ただし配線が面倒

- 基板を自作する

自作した事がないので挑戦してみたい。ただし難易度は高そう

- 基板発注

設計さえ出来ればあとはハンダ付けするだけ。海外に注文すれば安い。

ただし、私の語学力の問題とトライアンドエラーが出来ないのが問題かな?

後、腹案もいくつかありますが今の所この位考えています。

まあ、どれにしても設計は必要ですのでやってみます。

今回は基板自作も検討しているのでレイアウトまで出来る

「EAGLE」というツールを使ってみます。

EAGLEにはFMCコネクタのライブラリがないのでそのままでは作成できません。

FMCコネクタのライブラリを探すとzynqgeekさんがZedboad用のライブラリを公開されています。

https://github.com/zynqgeek

zed-board.lbrをダウンロードしてEAGLEに登録すると

FMCコネクタ(ASP-13604-01)とXADCが使えるようになります。

配置する際に気をつける事が回路図上で1個置いただけだと

半分の80ピンしか出てこないので2個置く必要があります。

2個おいてもレイアウトではちゃんと認識しています。

で、160ピン全部ピンヘッダに出したのが以下図

配線するのがかなり大変でした。

次はレイアウトをします。